Percobaan 1 kondisi 3

Buatlah sebuah rangkaian lengkap yang memuat 3 gerbang AND dengan 2 input

dan 3 input, kemudian gerbang OR dengan 2 dan 4 input, kemudian 1 gerbang

XOR dan 1 gerbang XNOR. Dan output akhir rangkaian keseluruhannya

ditunjukkan dengan LED atau LOGIC PROBE. Dimana input awal berupa 3

saklar SPDT.

2. Gambar Rangkaian Simulasi[Back] Percobaan 1 kondisi 3 sebelum run

Percobaan 1 kondisi 3

4. Prinsip Kerja Rangkaian[Back]

Percobaan 1 kondisi 3

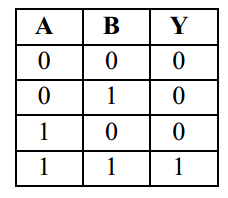

Memakai 3 kondisi dimana :

Kondisi 1 . A Berlogika 1, B berlogika 1, C berlogika 1, maka Output dari rangkaian berlogika 1

Dimana arus mengalir menuju AND U1 berlogika 1 dan 1 memiliki output logika 1, untuk AND U2 memiliki 3 input berlogika 1 dimana outputnya memiliki logika 1 lalu arus menuju OR U4 dimana memiliki 4 input semuanya berlogika 1 lalu outputnya berlogika 1 selanjutnya arus menuju AND U5 dimana inputnya berlogika 1 dan 1 lalu memiliki output 1, untuk XOR U3 arus memiliki 2 input dimana berlogika 1 dan outputnya berlogika 0 lalu menuju OR U6 yang inputnya berlogika 1 dan o lalu outputnya berlogika 1 selanjut nya menuju XNOR, karena XNOR mendapat Kedua input berlogika 1 maka output yang dihasilkan berlogika 1.

Kondisi 2 Ketika A Berlogika 1, B berlogika 0, C berlogika 1, maka output dari rangkaian berlogika 1

Dimana arus mengalir menuju AND U1 berlogika 1 dan 0 memiliki output logika 0, untuk AND U2 memiliki 3 input berlogika 1, 0, 1 dimana outputnya memiliki logika 0 lalu arus menuju OR U4 dimana memiliki 4 input berlogika 0, 1, 1, 0 lalu outputnya berlogika 1 selanjutnya arus menuju AND U5 dimana inputnya berlogika 1 dan 1 lalu memiliki output 1, untuk XOR U3 arus memiliki 2 input dimana berlogika 1, 0 dan outputnya berlogika 1 lalu menuju OR U6 yang inputnya berlogika 1 dan 1 lalu outputnya berlogika 1 selanjut nya menuju XNOR, karena XNOR mendapat Kedua input berlogika 1 maka output yang dihasilkan berlogika 1.

Kondisi 3. Ketika A Berlogika 0, B berlogika 0, C berlogika 0, maka output dari rangkaian berlogika 1

Dimana arus mengalir menuju AND U1 berlogika 0 dan 0 memiliki output logika 0, untuk AND U2 memiliki 3 input berlogika 0, 0, 0 dimana outputnya memiliki logika 0 lalu arus menuju OR U4 dimana memiliki 4 input berlogika 0, 0, 0, 0 lalu outputnya berlogika 0 selanjutnya arus menuju AND U5 dimana inputnya berlogika 0 dan 0 lalu memiliki output 0, untuk XOR U3 arus memiliki 2 input dimana berlogika 0, 0 dan outputnya berlogika 0 lalu menuju OR U6 yang inputnya berlogika 0 dan 0 lalu outputnya berlogika 0 selanjut nya menuju XNOR, karena XNOR mendapat Kedua input berlogika 0 maka output yang dihasilkan berlogika 1.

Link Download Rangkaian Percobaan 1 Kondisi 3

disiniLink Download Video modul 1 percobaan 1 kondisi 3

disiniLink download Datasheet Logic Probe

disiniLink download Datasheet Logic state

disini