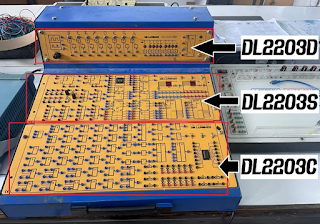

2. Alat dan Bahan

[Kembali]

Pada percobaan pertama JK flip-flop disusun secara seri ( counter asynchronous )dan input CLK dihubungkan ke clock. Arus dari SPDT dialirkan menuju setiap input RS pada setiap flip flop dan input JK pada input selanjutnya. Untuk flip-flop selanjut nyam aka akan dihubungkan ke output Q JK flip-flop sebelumnya, sehinga perubahan logicprobe berubah bergilir. Ketika rangkaian dijalankan dengan kondisi R dan S berlogika 1 atau mati karena R dan S aktif low, dan clock terhubung ke clock, maka rangkaian akan menghasilkan output bilangan biner 0-15 yang mana ini merupakan counter up.

5. Video Rangkaian [Kembali]

5. Video Rangkaian [Kembali]

1. Analisa sinyal output yang dikeluarkan masing-masing T flip flop? kenapa T flip terakhir disebut MSB?

pada percobaan yg di lakukan output yg di dapatkan bersifat toogle yg di pengaruhi oleh clock.clock di dalam rangkaian tersebut bersifat falltime dimana ketika input 1 menuju 0 maka hasilnya akan berbanding terbalik dari sebalikny.fliflop yg terakhir di sebut MSB karena menuju kepada bit terbesar.bit terbesar merupakan nilai yg tinggi karena flipflop terakhir

2. Analisa kondisi faltime dan risetime pada clock terhadap output pada percobaan yang dilakukan?

pada percobaan tersebut ketika kondisi rangkaian itu falltime maka outputny berubah dari 1 menuju 0 sedangkan risetime sebaliknya

7. Link Download

[Kembali]

.png)